# **GC-NIP**

# **Datasheet**

Version: 1.3 Date: 04/04/2017

+49 371 334204 - 0 +49 371 334204 - 69

E-Mail: info@amac-chemnitz.de

Web: www.amac-chemnitz.de

Tel.:

Fax:

# Revision history

| Date       | Revision | Changes                                          |

|------------|----------|--------------------------------------------------|

| 21/05/2013 | 1.0      | Initial version                                  |

| 17/06/2013 | 1.1      | Operating mode changes                           |

| 03/03/2014 | 1.2      | Characteristic values updated Updated schematics |

| 04/04/2017 | 1.3      | change to new AMAC document layout               |

### © Copyright 2017 AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH

Subject to change without prior notice.

Our policy is one of continuous improvement, and consequently the equipment may vary slightly from the description and specifications in this publication. The specifications, illustrations and descriptions provided in this documentation are not binding in detail. No part of this publication may be reproduced in any form, or by any means, without the prior written permission of AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH. All rights according to the law on copyright remain expressly reserved to AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH.

# **Contents**

| 1 Overview                                                               |    |

|--------------------------------------------------------------------------|----|

| 2 Features                                                               |    |

| 3 Ordering Information                                                   | 7  |

| 4 Typical applications                                                   | 8  |

| 5 Package                                                                | 9  |

| 6 Start up Behaviour / Configuration Options                             | 11 |

| 6.1 Reset                                                                | 11 |

| 6.2 Configuration                                                        | 12 |

| 7 Functional description                                                 |    |

| 7.1 Input amplifier / Low pass filter                                    | 14 |

| 7.2 Signal correction                                                    | 15 |

| 7.3 Interpolation / nonius calculation                                   |    |

| 7.3.1 Interpolation rate / nonius pitch                                  | 17 |

| 7.3.2 Edge distance control / Interval time t <sub>pp</sub> / Hysteresis |    |

| 7.3.3 Zero signal Z                                                      |    |

| 7.4 Maximum input frequency                                              |    |

| 7.5 Sensor monitoring                                                    |    |

| 7.6 Pins A/B/Z                                                           |    |

| 7.6.1 Standard ABZ (mode X000 and X010)                                  |    |

| 7.6.2 Controller / DSP (mode X001 and X011)                              | 22 |

| 7.6.3 Reference point adjustment (sensor adjustment Z - mode 0111)       |    |

| 7.6.4 Calibration mode (mode 0101)                                       |    |

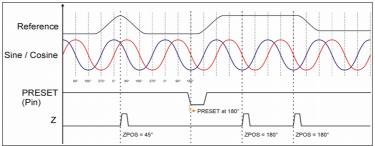

| 7.6.5 Sensor adjustment (mode 0101 and 0110)                             |    |

| 7.7 Measured value trigger                                               | 26 |

| 7.8 Measured value register POSIT, CNT, MVAL and STAT                    |    |

| 7.9 Count direction switch (pin DIR)                                     | 28 |

| 7.10 Counter preset / Nonius offset / Commands / Control signals         |    |

| 7.10.1 Nonius-Offset                                                     |    |

| 7.10.2 Configuration of the reference point position                     |    |

| 7.11 Power saving options                                                |    |

| 7.12 Signal propagation time                                             |    |

| 8 Digital interfaces                                                     |    |

| 8.1 Serial interface SPI                                                 |    |

| 8.1.1 Signals                                                            |    |

| 8.1.2 Protocol                                                           |    |

| 8.1.3 Register access                                                    |    |

| 8.1.4 Synchronous / asynchronous access                                  |    |

| 8.2 BiSS interface                                                       |    |

| 8.3 SSI interface                                                        |    |

| 8.4 Simple SPI Master                                                    |    |

| 8.5 EEPROM                                                               |    |

| 9 Register                                                               |    |

| 10 Characteristic values                                                 |    |

| 11 Application notes                                                     |    |

| 11.1 Application circuit                                                 |    |

| 11.2 Fast equidistant measurements via SPI                               |    |

| 11.3 Program sequence examples                                           |    |

| 11.4 EEPROM                                                              | 60 |

| 11.5 Evaluation of distance-coded reference marks                        |    |

| 11.6 Configuring t <sub>pp</sub> and f <sub>osz</sub>                    |    |

| 11.7 Configuration of the interface SPI/BiSS/SSI                         |    |

| 11.8 BiSS configuration file idbiss4743.xml                              |    |

| Notes                                                                    | 65 |

# List of figures

| Figure 1: F | Package QFN64                                      | 10     |

|-------------|----------------------------------------------------|--------|

| Figure 2: I | nput signals (single ended)                        | 14     |

|             | nput signals (differential)                        |        |

|             | CMIR (input signals)                               |        |

| Figure 5: I | nterpolation                                       | 16     |

| Figure 6: N | Nonius calculation                                 | 16     |

| Figure 7: E | Edge interval setting                              | 18     |

|             | Discretization of time                             |        |

|             | Digital hysteresis                                 |        |

|             | Interpolation (detail)                             |        |

|             | ABZ-Signals                                        |        |

| Figure 12:  | Adjustment of the reference (index) point          | <br>23 |

|             | Fine adjustment of the reference point position    |        |

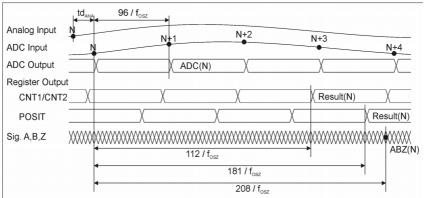

|             | Signal propagation time                            |        |

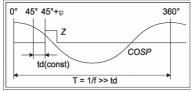

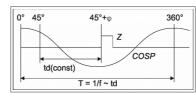

|             | Constant propagation delay                         |        |

|             | Constant propagation delay                         |        |

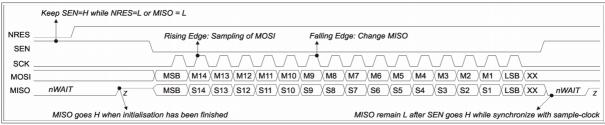

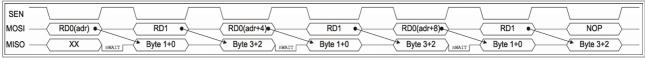

|             | SPI-transfer (1)                                   |        |

|             | SPI transfer (2)                                   |        |

|             | Write access 8 Bit.                                |        |

|             | Read access 32 Bit                                 |        |

|             |                                                    |        |

|             | Write access 32 Bit                                |        |

|             | Read access 3 x 32 Bit                             |        |

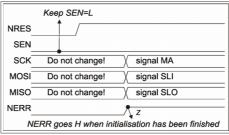

|             | BiSS interface initialization                      |        |

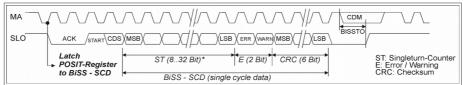

|             | BiSS SCD (Single Cycle Data)                       |        |

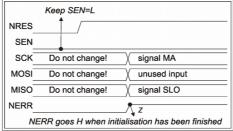

|             | SSI initialization                                 |        |

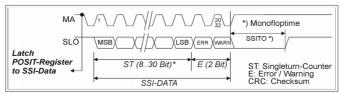

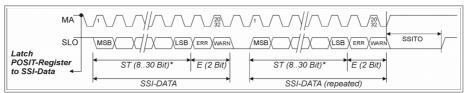

|             | SSI                                                |        |

| Figure 27:  | SSI (ring mode)                                    | 34     |

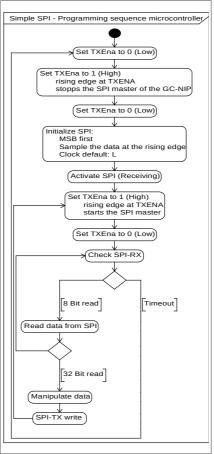

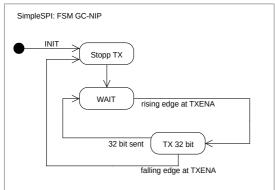

|             | Program sequence microcontroller                   |        |

|             | Program sequence GC-NIP                            |        |

|             | Simple SPI Master                                  |        |

|             | Timing SPI                                         |        |

|             | Sensor with differential output signals            |        |

|             | Sensor with a nominal amplitude of 1Vpp or 2Vpp    |        |

|             | Sensor with single-ended output signals (1)        |        |

|             | Sensor with single-ended output signals (2)        |        |

|             | Sensor containing antiparallel photodiodes         |        |

| Figure 37:  | Array of photo diodes with common cathode or anode | 55     |

| Figure 38:  | Sensor for current signals 11 µApp                 | 55     |

| Figure 39:  | ABZ Output / Configuration via pin                 | 56     |

| Figure 40:  | ABZ Output / Configuration via EEPROM              | 56     |

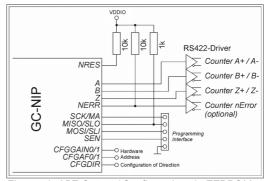

|             | SPI interface LVDS                                 |        |

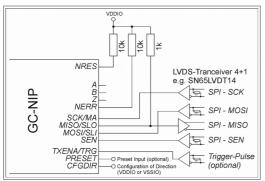

|             | SPI interface USB                                  |        |

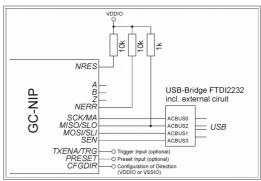

|             | BiSS interface                                     |        |

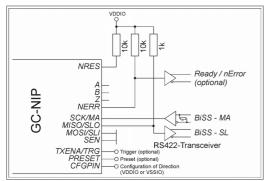

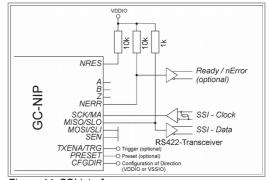

| _           | SSI interface                                      |        |

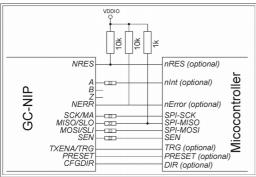

|             | SPI interface to microcontroller                   |        |

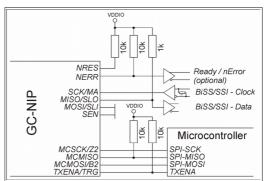

|             | SSI-/BiSS interface and Simple SPI master          |        |

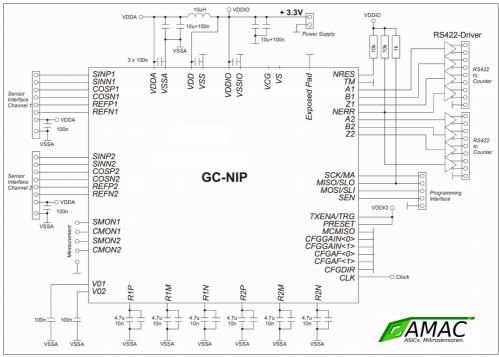

|             | Minimum application circuit (principle)            |        |

| Figure 48   | Program sequence for reading MVAL and STAT         | 59     |

|             | Extended programming sequence for ZMODE 10         |        |

|             | Extended programming sequence for ZMODE 11         |        |

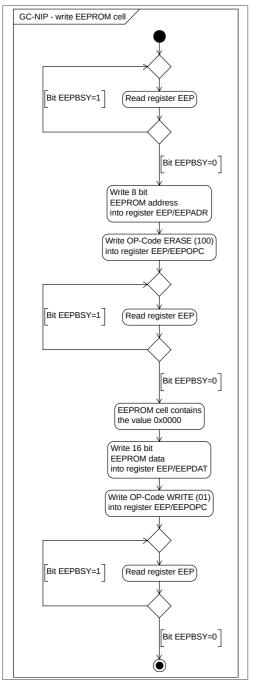

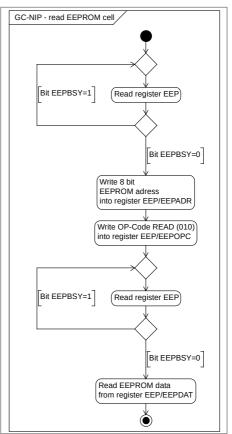

|             | Programming sequence write/read EEPROM             |        |

|             | Programming sequence write/read EEPROM             |        |

|             | Evaluation of distance-coded reference marks       |        |

| 94.0 00.    |                                                    | ٠,     |

### GC-NIP Datasheet

# List of tables

| Table 1: Applications overview                                        | Ω    |

|-----------------------------------------------------------------------|------|

| Table 2: Pin list QFN64                                               |      |

|                                                                       |      |

| Table 3: Selection of the serial interface                            |      |

| Table 4: switching the configuration source                           | . 11 |

| Table 5: Configuration of the interpolation rate and nonius pitch     | . 11 |

| Table 6: Configuration correction coefficients for nonius calculation |      |

| Table 7: Configuration options                                        |      |

| Table 8: Default configuration                                        |      |

| Table 9: Default configuration interfaces                             | .13  |

| Table 10: Configuration signal amplitude (nominal) (Register CFG1)    | .14  |

| Table 11: Configuration Low-pass-filter (Register CFG1)               | .14  |

| Table 12: Example: Common-mode input voltage (CMIR)                   | .15  |

| Table 13: Signal correction                                           | 15   |

| Table 14: Operating modes of the GC-NIP                               | .17  |

| Table 15: Selecting interpolation rate and nonius pitch               | .17  |

| Table 16: Maximum input frequency                                     |      |

| Table 17: Overview sensor monitoring                                  |      |

| Table 18: Recommended configuration of the sensor monitoring          | 20   |

| Table 19: ABZ modes                                                   | 22   |

| Table 20: DSP-Mode                                                    |      |

| Table 21: Reference point adjustment                                  |      |

| Table 22: Example: Reference point adjustment using the trigger mode  |      |

| Table 23: Sensor adjustment                                           |      |

| Table 24: Trigger mode / reference mode                               |      |

|                                                                       |      |

| Table 25: Measured value registers                                    |      |

| Table 26: Position data SSI/BiSS/SPI                                  |      |

| Table 27: Configuration of the position data register POSIT(31:0)     |      |

| Table 28: Configuration of the position data register MVAL(31:0)      |      |

| Table 29: Commands                                                    |      |

| Table 30: PRESET-Pin                                                  |      |

| Table 31: Nonius offset                                               |      |

| Table 32: PRESET-Pin CFG3/NOSEL = 1                                   |      |

| Table 33: Power saving options                                        |      |

| Table 34: Propagation delay analog (tdANA)                            |      |

| Table 35: Propagation delay digital (tdDIG)                           |      |

| Table 36: Register CFGBISS (BiSS mode)                                | .33  |

| Table 37: Default values BiSS register                                | 33   |

| Table 38: Register CFGBISS (SSI-Mode)                                 | .34  |

| Table 39: EEPROM addressing                                           |      |

| Table 40: Address mapping                                             |      |

| Table 41: Register overview                                           |      |

| Table 42: Absolute maximum ratings                                    |      |

| Table 43: Operating conditions                                        |      |

| Table 44: Characteristic values clock / reset                         |      |

| Table 45: Characteristic values for interpolation                     |      |

| Table 46: Digital characteristic values                               | 51   |

| Table 47: Analog characteristic values                                |      |

| Table 48: Characteristic values EEPROM                                |      |

| Table 49: Characteristic values SSI interface                         |      |

| Table 50: Characteristic values BiSS interface                        |      |

|                                                                       |      |

| Table 51: Characteristic values SPI interface                         |      |

| Table 52: Characteristic values Simple-SPI-Master                     |      |

| Table 53: IC connection, voltages                                     |      |

| Table 54: IC connection of unused in-/outputs                         |      |

| Table 55: Equidistant measurements                                    |      |

| Table 56: Evaluation of distance-coded reference marks                |      |

| Table 57: Configuration tpp and speed monitoring                      | 62   |

GC-NIP Datasheet Overview

## 1 Overview

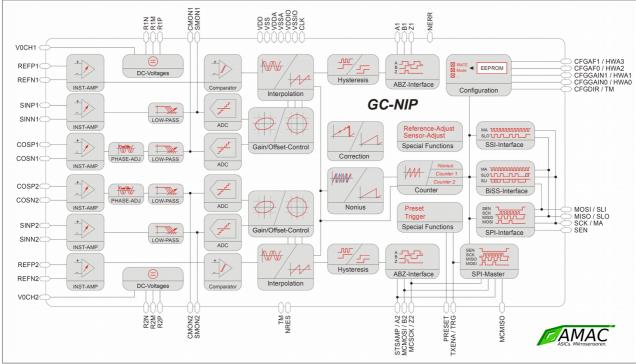

The 2-channel interpolation circuit GC-NIP serves to increase the resolution of absolute position and angular measuring systems with 2 sinusoidal output signals (nonius signal). Aside from the calculation of the absolute position, the GC-NIP may also operate as one- or two-channel incremental measuring system.

The input signals are subjected to an AMAC-specific internal gain and offset control. Additionally, the phase deviation of the input signals can be adjusted statically by a digital potentiometer.

Dividing the signal period of the input signals up to 8,192 times, the incremental position on both channels is calculated as well as the absolute position using the nonius calculation. For the absolute position of a two-channel nonius system, a resolution of up to 22 bit can be achieved.

The distance information can be passed on to processing components via a fast SPI interface, an SSI interface, a BiSS interface or by conventional ABZ-square-wave signals.

Input and output of the GC-NIP are designed for 3.3V interfaces. The IC comprises six instrumentation amplifiers with adjustable gain factors. Encoders with voltage interface or measuring bridges can be connected directly. Sensors with current interface and photodiode-arrays are adapted by a simple external circuit. The IC operates on both single-ended or differential input signals. The noise of the sensor signals is prevented by a switching analog filter. Additionally, a digital hysteresis can suppress the edge noise of the output signals at low input frequencies and at standstill. Thus, is case of short-time disturbance of the input signals, a subsequent interpolation counter will operate without errors.

The quality of the signals issued by the sensors is monitored in the IC. For that purpose it is possible to activate 9 sources separately producing an error signal. For the calculation of the absolute position a set of sensor- or scale-specific correction coefficients can be placed in the EEPROM of the IC. In that way, harmonics of the sinusoidal signals or inaccuracies of the measuring scale do not lead to errors in the absolute position value. The determination of the correction coefficients is realized by a simple software-based calibration procedure.

Providing absolute position and incremental square-wave-signals (ABZ) in parallel, the GC-NIP is well-suited for the use in motor-feedback-systems. The four integrated output interfaces (ABZ/SPI/SSI/BiSS) and further features like the multistage trigger signal processing, the processing of distance coded reference marks, the possibility to adjust the reference mark as well as adjustment and storage of the zero position make the IC suitable for direct use in industrial controls or in fast absolute or multichannel incremental position measuring systems. A selectable master SPI interface allows the user to modify the SSI/BiSS-data by providing additional information, for example data from an external multiturn counter or error information.

The GC-NIP can be configured according to specific applications using the integrated EEPROM, via configuration inputs or via the serial interface (SPI/BiSS).

Figure 1: block diagram

GC-NIP Datasheet Features

# 2 Features

| Interfaces                   |                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog input                 | Sinusoidal / cosinusoidal / reference (index) signals, differential or single-ended Adjustable amplification for 660 mV $_{PP}$ / 250 mV $_{PP}$ / 120 mV $_{PP}$ / 60 mV $_{PP}$ Input frequency max.130 kHz for nonius calculation; max. 90 kHz for interpolation                                                                                  |

| ABZ                          | 90° square-wave sequences (A/B/Z) Adjustable width of zero signal Z to ¼ or 1 period A/B Error signal; Interrupt signal for external processing Service signals for sensor adjustment                                                                                                                                                                |

| SPI                          | 30-bit counter value for the interpolation channels Up to 22-bit resolution for the absolute position 9-bit sensor status information on each channel Compatible to Standard-SPI: 16-bit, MSB first, up to 15 MHz                                                                                                                                    |

| SSI and BiSS                 | Up to 30-bit counter value 2-bit sensor status Gray code / binary code adjustable timing SSI ring operation                                                                                                                                                                                                                                          |

| Additional inputs            | Trigger input for storage of the measured value Preset signal for adjustment and storage of the counter values Reference position alignment using external signal                                                                                                                                                                                    |

| Configuration options        | Integrated EEPROM Configuration inputs Serial Interface (SPI/BiSS)                                                                                                                                                                                                                                                                                   |

| Interpolation / nonius calcu | lation / signal processing                                                                                                                                                                                                                                                                                                                           |

| Interpolation rate           | 256 to 8192, divisible by 8<br>Adjustable Divider 1/2/4/8 for the AB-signals on each channel                                                                                                                                                                                                                                                         |

| Nonius pitch                 | Number of periods per turn for absolute position calculation<br>Interpolation rate / [8 / 16 / 32 / 64]                                                                                                                                                                                                                                              |

| Nonius correction            | Correction coefficients stored in EEPROM<br>Software based calibration process for determination of the correction coefficients                                                                                                                                                                                                                      |

| Signal correction            | AMAC-specific digital controller for the offset, control range ±10% of the standard amplitude AMAC-specific digital controller for the amplitude, control range 60% 120% of the standard amplitude Digital potentiometer with 64 steps for phase correction; selectable range ±5° or ±10° Input signal monitoring with configurable error indication |

| Suppression of disturbances  | Adjustable low pass filter 10 kHz, 75 kHz, 150 kHz Digital hysteresis for suppression of the edge noise at the output (configurable 07) Selectable minimum edge distance at the output (bandwidth limitation)                                                                                                                                        |

| Reference signal processing  | Adjustable reference mark position in 32 steps 0 360° Optional: high precision alignment of the reference mark position (configuration via external signal possible) Processing of distance coded reference marks Measured-value trigger at the reference mark position                                                                              |

| Miscellaneous                | Optional Master-SPI interface for output and manipulation of SSI/BiSS-Data 2-stage measured value trigger Constant delay between sampling and measurement value for all resolutions                                                                                                                                                                  |

| Important characteristics    |                                                                                                                                                                                                                                                                                                                                                      |

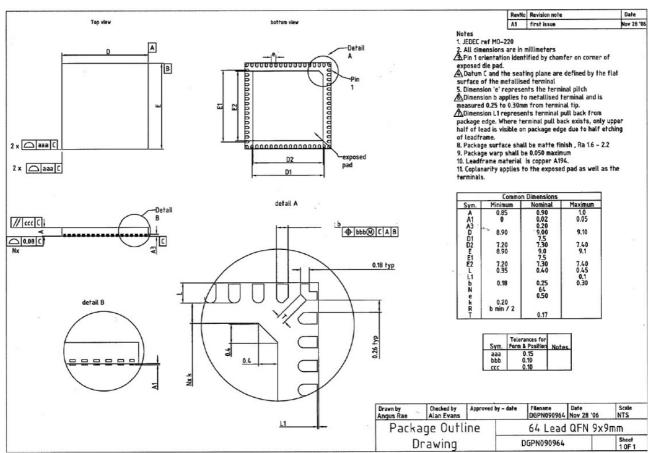

| Package                      | QFN64 (9 x 9 mm)                                                                                                                                                                                                                                                                                                                                     |

| Operating voltage            | 3.3V                                                                                                                                                                                                                                                                                                                                                 |

| Temperature range            | -40 125 °C                                                                                                                                                                                                                                                                                                                                           |

| Max interface clock          | SPI 15 MHz, BiSS 10 MHz, SSI 5 MHz                                                                                                                                                                                                                                                                                                                   |

# 3 Ordering Information

| Product Type         | Description                                        | Article Number |

|----------------------|----------------------------------------------------|----------------|

| GC-NIP               | Interpolation Circuit GC-NIP, QFN64                | PR-44800-00    |

| GC-LS                | 4-channel / analog Level-Shifter 5V to 3.3V, QFN32 | PR-44500-00    |

| GP-NIP               | Demoboard for Interpolation circuit GC-NIP         | PR-44810-00    |

| USB to SPI converter | USB adapter for the SPI interface                  | PR-44025-10    |

Document: 44800-DB-1-3-E-NIP-AMAC Page: 7/65

GC-NIP Datasheet Typical applications

# 4 Typical applications

Table 1: Applications overview

| Signal form (Sensor)                               | Application of GC-NIP                                           |

|----------------------------------------------------|-----------------------------------------------------------------|

| Sinusoidal, Voltage                                | Direct connection of GC-NIP to sensor.                          |

| Sinusoidal, Current                                | Additional resistors required                                   |

| Reference- (Index-) Track                          | Direct connection of GC-NIP to sensor.                          |

| Square wave                                        | IC is not suitable in principle.                                |

| Signal Form (Sensor)                               | Application of GC-NIP                                           |

| 1 V <sub>pp</sub> nominal                          | Use GC-LS for signal conversion or external resistors.          |

| 660 mV <sub>pp</sub> nominal                       | Direct connection of GC-NIP to sensor.                          |

| 330 mV <sub>pp</sub> nominal                       | Use GC-LS for signal conversion or external resistors.          |

| 250 mV <sub>pp</sub> nominal                       | Direct connection of GC-NIP to sensor.                          |

| 120 mV <sub>pp</sub> nominal                       | Direct connection of GC-NIP to sensor.                          |

| 80 mV <sub>pp</sub> nominal                        | Use GC-LS for signal conversion or external resistors.          |

| 60 mV <sub>pp</sub> nominal                        | Direct connection of GC-NIP to sensor.                          |

| 2 V <sub>pp</sub> nominal                          | External resistors required (see 11).                           |

| Differential signal, DC-Reference Voltage 0.821.8V | Direct connection of GC-NIP to sensor.                          |

| Single-Ended, DC-Reference Source in Sensor        | Direct connection of GC-NIP to sensor.                          |

| Single-Ended, DC-Reference Source not in Sensor    | Direct connection of GC-NIP to sensor.                          |

| Photodiodes 0.5 μA <sub>pp</sub>                   | External resistors required. (see 11).                          |

| Photodiodes 11 $\mu A_{pp}$ 16 $\mu A_{pp}$        | External resistors required. (see 11).                          |

| Resistive bridges (magnetic sensors)               | Direct connection of GC-NIP to sensor.                          |

| Unstable amplitude of sensor                       | GC-NIP contains automatic controller for amplitudes.            |

| Offset not correctable at sensor                   | GC-NIP contains automatic controller for offset.                |

| Phase not correctable at sensor                    | GC-NIP contains potentiometer for phase correction.             |

| Variable Reference mark position                   | Reference mark position is freely adjustable.                   |

| Distance coded reference marks                     | Evaluation support via SPI using the internal trigger-function. |

| Subsequent processing                        | Application of GC-NIP                                                                                |

|----------------------------------------------|------------------------------------------------------------------------------------------------------|

| Interface to microcontroller/DSP/FPGA        | Use SPI-Interface                                                                                    |

| Interface to external interpolation counter  | AB-Interface for both channels                                                                       |

| Usage on industrial control                  | SSI, BiSS or ABZ-Interface                                                                           |

| System includes more than one channel        | 2 incremental interpolation channels included. Possibility to use simultaneously on only one SPI-Bus |

| Real-Time-System / equidistantly measurement | Constant propagation delay for all resolutions, trigger input                                        |

| IC-Configuration                             | Integrated EEPROM, all registers are configurable via SPI/BiSS                                       |

| Signal specification LVCMOS                  | In-/Outputs used directly                                                                            |

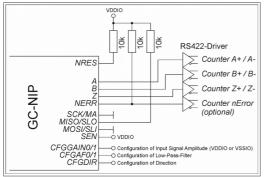

| Signal specification RS422                   | Driver-IC required                                                                                   |

| Maximum signal frequencies                          |                                                                               |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| Rotary encoder: $f_{max} =$                         | (revolutions / minute)·(signal periods / revolution) / 60                     |  |  |  |  |

| Linear encoder: fr                                  | <sub>max</sub> = (v <sub>MAX</sub> [in m/s] / (signal periods [in mm]) · 1000 |  |  |  |  |

| f <sub>max</sub> < 150 kHz                          | All interpolation rates up to 8192 via SPI/SSI/BiSS                           |  |  |  |  |

| f <sub>max</sub> < 23 MHz / Interpolation rate      | If ABZ-outputs are used                                                       |  |  |  |  |

| Max frequency of interpolation counter on ABZ known | Configuration of the minimum edge distance possible via CFGTPP                |  |  |  |  |

Document: 44800-DB-1-3-E-NIP-AMAC Page: 8/65

GC-NIP Datasheet Package

# 5 Package

Table 2: Pin list QFN64

| Pin | Name              | Туре                            | Description                                                                |  |  |  |  |

|-----|-------------------|---------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| 1   | VDDA              | Power                           | Supply voltage analog +3.3V                                                |  |  |  |  |

| 2   | VSSA              | Power                           | Analog GND                                                                 |  |  |  |  |

| 3   | R2P               | Analog                          | ADC2-reference voltage high                                                |  |  |  |  |

| 4   | R2M               | Analog                          | ADC2-reference voltage mid                                                 |  |  |  |  |

| 5   | R2N               | Analog                          | ADC2-reference voltage low                                                 |  |  |  |  |

| 6   | SMON2             | Output analog (Buffer)          | Monitor Output at instrumentation amplifier sine channel 2                 |  |  |  |  |

| 7   | CMON2             | Output analog (Buffer)          | Monitor Output at instrumentation amplifier cosine channel 2               |  |  |  |  |

| 8   | N.C.              | n.c.                            | Do not connect                                                             |  |  |  |  |

| 9   | VDD               | Power                           | Supply voltage digital +3.3V                                               |  |  |  |  |

| 10  | VSS               | Power                           | Digital GND                                                                |  |  |  |  |

| 11  | CFGAF1/HWA3       | Input digital / Pull-Down       | Configuration analog filter / HWA<3>                                       |  |  |  |  |

| 12  | CFGAF0/HWA2       | Input digital / Pull-Down       | Configuration analog filter / HWA<2>                                       |  |  |  |  |

| 13  | SCK/MA            | Input digital / Pull-Down       | SPI/BiSS/SSI: clock                                                        |  |  |  |  |

| 14  | SEN               | Input digital / Pull-Up         | SPI: select / during Reset: select interface SPI / BiSS or SSI             |  |  |  |  |

| 15  | MOSI/SLI          | Input digital / Pull-Down       | SPI/BiSS: data in GC-NIP                                                   |  |  |  |  |

| 16  | MISO/SLO          | -                               | SPI/BiSS/SSI: data out GC-NIP                                              |  |  |  |  |

| 17  | N.C.              | n.c.                            | Do not connect                                                             |  |  |  |  |

| 18  | VDDIO             | Power                           | Supply voltage digital (IO) +3.3V                                          |  |  |  |  |

| 19  | VSSIO             | Power                           | Digital GND                                                                |  |  |  |  |

| 20  | MCSCK / Z2        | Output Digital / Tristate       | Controller interface – clock / Output for Zero signal Z (reference signal) |  |  |  |  |

| 21  | MCMOSI / B2       | Output Digital / Tristate       | Controller interface – data out / Incremental output B channel 2           |  |  |  |  |

| 22  | STSAMP / A2       | Output Digital / Tristate       | Controller interface – sync signal / Incremental output A channel 2        |  |  |  |  |

| 23  | MCMISO            | Input Digital                   | Controller interface – data in                                             |  |  |  |  |

| 24  | TXENA / TRG       | Input Digital                   | Controller interface – enable / trigger                                    |  |  |  |  |

| 25  | CLK               | Clock-Input                     | Clock                                                                      |  |  |  |  |

| 26  | PRESET            | Input digital / Pull-Up         | Input for the preset function                                              |  |  |  |  |

| 27  | CFGDIR / TM2      | Input digital / Pull-Down       | config. count direction nonius                                             |  |  |  |  |

| 28  | Z1                | Output Digital / Tristate       | Output for Zero signal Z (reference signal) channel 1                      |  |  |  |  |

| 29  | B1                | Output Digital / Tristate       | Incremental Output B channel 1                                             |  |  |  |  |

| 30  | A1                | Output Digital / Tristate       | Incremental Output A channel 1                                             |  |  |  |  |

| 31  | VSSIO             | Power                           | Digital GND                                                                |  |  |  |  |

| 32  | VDDIO             | Power                           | Supply Voltage digital (IO) +3.3V                                          |  |  |  |  |

| 33  | NERR              | Output Digital / Open-<br>Drain | Error signal                                                               |  |  |  |  |

| 34  | CFGGAIN0/HWA      | Input digital / Pull-Down       | Configuration Gain / HWA<0>                                                |  |  |  |  |

| 35  | CFGGAIN1/HWA<br>1 | Input digital / Pull-Down       | Configuration Gain / HWA<1>                                                |  |  |  |  |

| 36  | TM                | Input digital                   | Test mode; Connect to VSS                                                  |  |  |  |  |

| 37  | NRES              | In-/Output analog; Pull-Up      | Reset                                                                      |  |  |  |  |

| 38  | VS                | Power                           | Test EEPROM                                                                |  |  |  |  |

| 39  | VCG               | Power                           | Test EEPROM                                                                |  |  |  |  |

| 40  | VSS               | Power                           | Digital GND                                                                |  |  |  |  |

| 41  | VDD               | Power                           | Supply voltage digital +3.3V                                               |  |  |  |  |

| 42  | CMON1             | Output analog (Buffer)          | Monitor Output at instrumentation amplifier cosine channel 1               |  |  |  |  |

| 43  | SMON1             | Output analog (Buffer)          | Monitor Output at instrumentation amplifier sine channel 1                 |  |  |  |  |

| 44  | R1N               | Analog                          | ADC1-reference voltage low                                                 |  |  |  |  |

| 45  | R1M               | Analog                          | ADC1-reference voltage mid                                                 |  |  |  |  |

| 46  | R1P               | Analog                          | ADC1-reference voltage high                                                |  |  |  |  |

|     |                   | 9                               | <u> </u>                                                                   |  |  |  |  |

Document: 44800-DB-1-3-E-NIP-AMAC Page: 9/65

GC-NIP Datasheet Package

| 47  | VSSA  | Power                  | Analog GND                                       |

|-----|-------|------------------------|--------------------------------------------------|

| 48  | VDDA  | Power                  | Supply voltage analog +3.3V                      |

| 49  | N.C.  | n.c.                   | Do not connect                                   |

| 50  | REFP2 | Input analog           | Input Reference Signal positive channel 2        |

| 51  | REFN2 | Input analog           | Input Reference Signal negative channel 2        |

| 52  | REFP1 | Input analog           | Input Reference Signal positive channel 1        |

| 53  | REFN1 | Input analog           | Input Reference Signal negative channel 1        |

| 54  | V0CH1 | Output analog (Buffer) | Mean voltage channel 1                           |

| 55  | SINP1 | Input analog           | Sinusoidal signal at input, positive channel 1   |

| 56  | SINN1 | Input analog           | Sinusoidal signal at input, negative channel 1   |

| 57  | COSN1 | Input analog           | Cosinusoidal signal at input, negative channel 1 |

| 58  | COSP1 | Input analog           | Cosinusoidal signal at input, positive channel 1 |

| 59  | COSP2 | Input analog           | Cosinusoidal signal at input, positive channel 2 |

| 60  | COSN2 | Input analog           | Cosinusoidal signal at input, negative channel 2 |

| 61  | SINN2 | Input analog           | Sinusoidal signal at input, negative channel 1   |

| 62  | SINP2 | Input analog           | Sinusoidal signal at input, positive channel 1   |

| 63  | V0CH2 | Output analog (Buffer) | Mean voltage channel 2                           |

| 64  | N.C.  | n.c.                   | Do not connect                                   |

| EXP | VSS   | Exposed Pad            | Digital GND                                      |

Figure 1: Package QFN64

# 6 Start up Behaviour / Configuration Options

#### 6.1 Reset

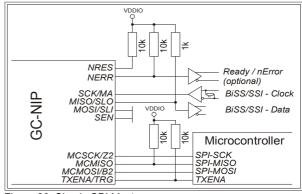

During reset of the IC, the digital interface is selected (SPI or SSI/BiSS) and all registers are initialized with their default values. The initialization of the circuit is performed either from the internal EEPROM or from configuration pins. The internal EEPROM has to be programmed with a valid identifier at EEPROM address 0x00 to be used for configuration after reset. The configuration of the interpolation rate is either done from the EEPROM (if valid) or with a fixed interpolation rate of 2000. Another valid identifier on EEPROM address 0x01 decides, if the correction coefficients – also located in the EEPROM of the IC – are loaded during reset and be used for absolute position calculation.

During the whole reset sequence, a pin - dependent on the selected interface - NERR or MISO, is maintained at L level. Up to this point, the serial interfaces may not be activated. Subsequently, the configuration registers can be modified using the SPI- or BiSS-interface. The following tables provide an overview of the configuration possibilities for the GC-NIP.

Table 3: Selection of the serial interface

| Interface | Pin SEN reset value | BIT SSI 1) | Pin MISO / SLO | Pin MOSI / SLI | Pin SCK | Pin SEN | Ready-Signal |

|-----------|---------------------|------------|----------------|----------------|---------|---------|--------------|

| SPI       | 1                   | any value  | SPI-MISO       | SPI-MOSI       | SPI-SCK | SPI-SEN | at MISO      |

| SSI       | 0                   | 1          | SSI-DATA       | -              | SSI-MA  | 0       | at NERR      |

| BiSS      | 0                   | 0          | BiSS-SLO       | BiSS-SLI       | BiSS-MA | 0       | at NERR      |

<sup>1)</sup> Register CFGBiSS / Bit 31

Table 4: switching the configuration source

| Content of EEPROM address 0x00 | Configuration                                  |

|--------------------------------|------------------------------------------------|

| unequal 0x134A                 | Basic configuration / see Tables 8 and 9 (Pin) |

| 0x134A                         | read from EEPROM / Tables 8 and 9 (EEPROM)     |

Table 5: Configuration of the interpolation rate and nonius pitch

| Content of EEPROM address 0x00 | Bit IRMAP 1)        | Configuratio<br>n Source | Interpolation rate IRATE                 | Nonius pitch<br>(Signal on channel 1) | Interpolation rate ABZ |

|--------------------------------|---------------------|--------------------------|------------------------------------------|---------------------------------------|------------------------|

| unequal 0x134A                 | default value:<br>1 | Manufacturer<br>EEPROM   | 2000                                     | 125                                   | 2000                   |

| 0x134A                         | 0                   | EEPROM                   | any between [256 8192]<br>divisible by 8 | IRATE / [16,32,64, 128]               | IRATE / [1,2,4,8]      |

| 0x134A                         | 1                   | Manufacturer<br>EEPROM   | 2000                                     | 125                                   | 2000 / [1,2,4,8]       |

<sup>1)</sup> Register CFG1 / Bit 3

Table 6: Configuration correction coefficients for nonius calculation

| Content of EEPROM address 0x01 | correction coefficients value |

|--------------------------------|-------------------------------|

| unequal 0x134A                 | All 0                         |

| 0x134A                         | Read from EEPROM              |

## 6.2 Configuration

The IC can be matched to most varied measuring systems and subsequent electronic systems by way of the configuration registers. If the IC is initialized using the integrated EEPROM or a serial interface (SPI/BiSS), full configuration possibilities are available. If the initialization is performed via the configuration pins, selected parameters can be set externally. Table 7 below provides an overview of the configuration possibilities of the GC-NIP. Detailed description of the configuration register set can be found in sector 9 of this document.

Table 7: Configuration options

| Parameter                          | Possible values                                                                                                                                                                                 | Register / Bit                                                                                                                                                     |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interpolation rate IRATE           | Configurable interpolation table in EEPROM Alternative: fixed table in manufacturer-PROM Divider for square-wave-signals (ABZ) and counter Separate divider for channel 1 and 2                 | From EEPROM<br>CFG1 / IRMAP<br>CFG1 / IRDIV(1:0)<br>CFG1 / IRD2SEL, CFG3 / IRDIV2(1:0)                                                                             |

| Operating mode                     | Nonius + ABZ 2 Channel<br>Calibration Mode                                                                                                                                                      | CFG1 / MODE(3:0)                                                                                                                                                   |

| Nonius pitch                       | Interpolation rate / [8 / 16 / 32 / 64]                                                                                                                                                         | From EEPROM                                                                                                                                                        |

| Nonius correction                  | Correction values Correction value resolution Activate / deactivate correction                                                                                                                  | From EEPROM<br>CFG3 / MXSHR<br>CFG3 / MXFEED                                                                                                                       |

| Min. edge interval t <sub>pp</sub> | 1, 2, 4, 8, 16, 32, 64, 128                                                                                                                                                                     | CFG1 / CFGTPP(2:0)                                                                                                                                                 |

| Reference point                    | Enable, Disable, Delayed<br>Width 1 Increment / 4 Increments<br>Position 0°-360°, step size 11.25°<br>Mode Reset, Trigger, adjust, distance coded<br>Position 0°-360°, step size 360°/IRATE     | CFG3 / DISZ(1:0), CFG3 /ZDEL(1:0)<br>CFG2 / Z4<br>CFG2 / ZPOS<br>CFG2 / ZMODE<br>CFG3/NOSEL, NONOFFS                                                               |

| Nominal signal amplitude           | 660 mV <sub>pp</sub> , 250 mV <sub>pp</sub> , 120 mV <sub>pp</sub> , 60 mV <sub>pp</sub>                                                                                                        | CFG1 / GAIN(1:0)<br>alternative: Pins CFGGAIN(1:0)                                                                                                                 |

| Low pass filter (1dB)              | 150kHz, 75kHz, 10kHz (all +/-10%), Disable                                                                                                                                                      | CFG1 / CFGAF<br>alternative: Pins CFGAF(1:0)                                                                                                                       |

| Digital hysteresis                 | 0 (Disable), 1 7                                                                                                                                                                                | CFG3 / DH(2:0)                                                                                                                                                     |

| Output signals A/B/Z               | ABZ-Mode, DSP-Mode, sensor adjustment,<br>Reference mark adjustment<br>Optional Master-SPI on ABZ-channel 2                                                                                     | CFG1 / MODE(2:0) CFG1 / MODE(3)                                                                                                                                    |

| Error processing                   | Masking, latch enable Output configuration in case of errors                                                                                                                                    | CFG1 / Mxxx, Lxxx<br>CFG1 / HLD, TRI                                                                                                                               |

| Phase correction                   | ± 10° step width 0.15°, ±5° step width 0.08°                                                                                                                                                    | CFG2 / PH1(5:0)<br>CFG2 / PH2(5:0)<br>CFG2 / PHBER,                                                                                                                |

| Gain controller                    | Default setting / time constant / Enable, Disable                                                                                                                                               | CNTRLG, CFG3 / GAINCTL, DISCTL                                                                                                                                     |

| Offset controller                  | Default setting / time constant / Enable, Disable                                                                                                                                               | CNTRLO, CFG3 / OFFSCTL, DISCTL                                                                                                                                     |

| Hardware address                   | 0-15                                                                                                                                                                                            | CMD / SETHWA<br>Pins HWA(3:0)                                                                                                                                      |

| Special functions                  | Trigger pulse edge Preset function active / inactive Absolute position offset Counter preset position Absolute counter direction                                                                | CFG1 / TRGSLP<br>CFG2 / PREENA<br>NONOFFS, PREST2<br>PREST1,PREST2<br>Pin CFGDIR                                                                                   |

| Interface configuration            | Format of the position values SPI-Mode synchronous, asynchronous BISS interface active, inactive SSI-Timing BISS-Timing BISS data format 8Bit, 32 Bit SPI for manipulation of the SSI/BISS-Data | CFGBISS / SSI20, GRAY, STBIT, STSEL<br>CFG2 / ASYNC, SYNC(6:0)<br>CFGBISS / SSI<br>CFGBISS / SSITO, RING<br>CFGBISS / BISSTO<br>CFGBISS / READ32<br>CFG1 / MODE(3) |

| Power saving options               | Deactivation of the Monitor-outputs Deactivation V0-Pins Deactivation of Channel 2 Deactivation of the nonius correction Deactivation of the reference mark processing                          | CFG2 / DISMON<br>CFG2 / DISV0<br>CFG3 / DISCH2<br>CFG3 / MXFEED<br>CFG3 / DISZ1, DISZ2                                                                             |

#### **GC-NIP Datasheet**

Table 8: Default configuration

| Configuration           | Default (EEPROM with fact                                                                                                                  | ory settings)                                                                  | Default (Pin)                                                                                                                               |                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Analog                  | Phase correction<br>Low pass -1dB<br>Nominal signal amplitude<br>Power saving options                                                      | 0°<br>150 kHz<br>660 mVpp<br>inactive                                          | Phase correction<br>Low pass -1dB<br>Nominal signal amplitude<br>Power saving options                                                       | 0°<br>configured via pin<br>configured via pin<br>inactive                     |

| Interpolation<br>Nonius | Interpolation rate Controller Controller start values Reference mark position Nonius pitch Correction Count direction Power saving options | 8000 active, timing 01 Average at 45° 125 none configured via pin DIR inactive | Interpolation rate Controller Controller start values Reference mark position Nonius pitch Correction Count direction Powers saving options | 2000 active, Timing 01 Average at 45° 125 none configured via pin DIR inactive |

| ABZ output signals      | Mode TPP Digital hysteresis Z Output in case of error Power saving options                                                                 | ABZ<br>0<br>1<br>active, 1 increment<br>Hold<br>inactive                       | Mode TPP Digital hysteresis Z Output in case of error Power saving options                                                                  | ABZ<br>0<br>1<br>active, 1 increment<br>Hold<br>inactive                       |

| Error processing        | Error monitoring<br>Error storage                                                                                                          | all errors inactive                                                            | Error monitoring<br>Error storage                                                                                                           | all errors inactive                                                            |

| Special functions       | Preset (Nonius) Preset values Nonius offset Trigger pulse edge                                                                             | inactive<br>0x00<br>0x00<br>falling                                            | Preset (Nonius) Preset values Nonius offset Trigger pulse edge                                                                              | always inactive<br>0x00<br>0x00<br>falling                                     |

Table 9: Default configuration interfaces

| rable 9: Default cor | inguration interfaces                                                                                       |                                                                                                              |

|----------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Configuration        | Default (EEPROM with factory settings)                                                                      | Default (Pin)                                                                                                |

| SPI interface        | Activate via Pin SEN Hardware-address at HWA (3:0)                                                          | Activate via Pin SEN Hardware-address at HWA (3:0)                                                           |

| SSI interface        | Activate via Pin SEN Timeout 20 µs @ 26 MHz, Ring mode Format 20Bit Direct output (no Simple-SPI)           | Activate via Pin SEN Timeout 20 μs @ 26 MHz, Ring mode Format 20Bit Direct output (no Simple-SPI)            |

| BiSS interface       | Hardware-address at HWA (3:0) Timeout 19.7 µs @ 26MHz Format 30Bit Singleturn Direct output (no Simple-SPI) | Hardware-address at HWA (3:0) Timeout 19.6 µs @ 26 MHz Format 30Bit Singleturn Direct output (no Simple-SPI) |

## 7 Functional description

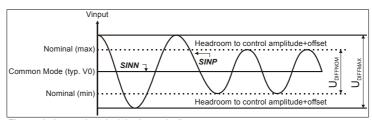

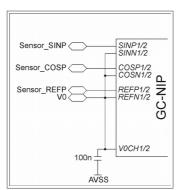

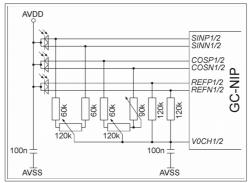

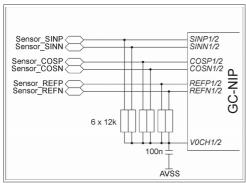

## 7.1 Input amplifier / Low pass filter

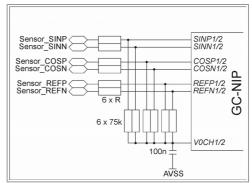

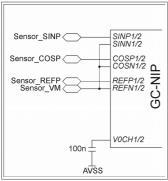

The GC-NIP incorporates six instrumentation amplifiers with adjustable gain factors. Incremental encoders with voltage interface and measuring bridges can be connected directly. Sensors with current-interface are adapted by way of a simple external circuit (see 11.1). The IC operates with both, single-ended and differential input signals. The amplification is identical for all signals of the sensor (sinusoidal, cosinusoidal, index/reference). To adapt the GC-NIP to customized sensors, the mean voltage of the instrumentation amplifiers is provided at pins V01 and V02.

The instrumentation amplifiers are connected to the internal AD converters. Alternatively, this connection is done directly or via a configurable low-pass filter. The cut-off frequencies given in Table 11 are achieved with an accuracy of  $\pm 10\%$ . The conversion range of the analog-digital-converter and the reference voltages of the instrumentation amplifiers are pre-adjusted, so that internal offset-error are already compensated. The signals on the input of the analog-digital-converters can be monitored using the pins SMON1, CMON1, SMON2 and CMON2<sup>1</sup>.

Table 10: Configuration signal amplitude (nominal) (Register CFG1)

| CFG1/GAIN(1:0)                                                               | 00     | 01     | 10    | 11   |

|------------------------------------------------------------------------------|--------|--------|-------|------|

| Input voltage for differential supply ¹¹(mV <sub>pp</sub> )                  | 330    | 125    | 60    | 30   |

| Input voltage U <sub>DiffNom</sub> nominal (mV <sub>pp</sub> )               | 660    | 250    | 120   | 60   |

| Input voltage range for $U_{Diff}$ (mV <sub>pp</sub> )                       | 400800 | 150300 | 75145 | 3672 |

| Input voltage for maximal ADC-range U <sub>DiffMAX</sub> (mV <sub>pp</sub> ) | 990    | 375    | 180   | 90   |

| Reference voltage on V0 nominal                                              | 1.1    | 1.1    | 1.1   | 1.1  |

| Output voltage $U_{MON}$ nominal on SMON / CMON ( $V_{pp}$ )                 | 1.27   | 1.27   | 1.27  | 1.27 |

| Amplification (U <sub>MON</sub> /U <sub>DIFF</sub> )                         | 1.92   | 5.08   | 10.6  | 21.2 |

<sup>1)</sup> at each of the inputs SINP, SINN, COSP, COSN

Table 11: Configuration Low-pass-filter (Register CFG1)

| Cut-Off-Frequency -1dB | CFG1/CFGAF(1:0) |

|------------------------|-----------------|

| 150 kHz (-0.5dB)       | 00              |

| 75 kHz                 | 01              |

| 10 kHz                 | 10              |

| low-pass disabled      | 11              |

Figure 2: Input signals (single ended)

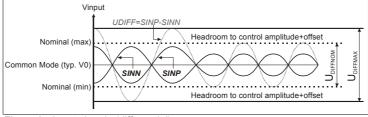

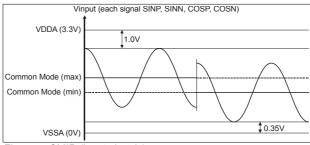

Figure 3: Input signals (differential)

Document: 44800-DB-1-3-E-NIP-AMAC

Page: 14/65

<sup>1</sup>The analog low-pass-filter must be activated when using the monitor-outputs (CFG1/CFGAF ≠ '11').

The input voltage for the instrumentation amplifiers is limited in a range from  $V_{in}$ =0.35V to VDDA-1.00V. According to the common-mode-voltage at the analog input, this may limit the operating range for the Gain-Configuration "00" ( $V_{NOM}$  = 660 m $V_{pp}$ ).

Figure 4: CMIR (input signals)

Exemplary, the following table shows combinations for common-mode-voltage and supply voltage for single-ended input signals with maximum amplitude of  $880 \text{mV}_{pp}$  and maximum offset of  $\pm 70 \text{ mV}$ :

Table 12: Example: Common-mode input voltage (CMIR)

| VDDA  | Common-mode voltage (Min) | Common-mode voltage (Max) |

|-------|---------------------------|---------------------------|

| 3.30V | 0.82V                     | 1.83V                     |

| 3.15V | 0.82V                     | 1.63V                     |

| 3.00V | 0.82V                     | 1.53V                     |

## 7.2 Signal correction

The input signals are subjected to an AMAC-specific internal gain and offset control. The amplitudes are controlled in the range between 60 % and 120 % of the standard amplitude. The control range for the offset of the two input signals is  $\pm$  10% of the nominal amplitude. The phase displacement of the input signals can be corrected statically in 64 steps using a digital potentiometer. The setting range of the phase is set to approx. +/-5 $^{\circ}$  or approx. +/-10 $^{\circ}$  by way of a configuration bit.

After resetting the IC, start values to correct amplitude and offset of the input signals are loaded from the EEPROM. If the EEPROM content is not marked valid (see 4), these values are set to the center of the control range. The full measuring accuracy of the IC, however, is only achieved after settling of the internal signal control after about 10...50 periods of the input signals. Alternatively, start values for the controller can be stored in EEPROM, so that the settling time of the controller after reset of the IC can be shortened.

To achieve the maximum possible accuracy in the amplitude and offset control, the phase potentiometer must be matched with the sensor connected to the GC-NIP. Amplitude and offset errors are treated as a unit in the GC-NIP. This means that for particular applications a larger permissible error may be permitted for the respectively other parameter under certain circumstances. The attenuation of the controlled system implemented in the GC-NIP can be adjusted (registers CFG3/GAINCTL and CFG3/OFFSCTL).

Table 13: Signal correction

| Parameter                                               | as a percentage<br>referred to the<br>nominal amplitude<br>(PEAK-PEAK) | as a percentage<br>referred to the<br>ADC-maximum<br>(PEAK-PEAK) | in mV referred to<br>the standard<br>signal<br>(0.66 Vpp) | in V on the pin<br>SMON and CMON<br>(PEAK-PEAK) |

|---------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|

| Maximal value at the input (Vmax <sub>pp</sub> )        | 150                                                                    | 100                                                              | 990                                                       | 1.90                                            |

| Nominal value of the input signal (Vnom <sub>pp</sub> ) | 100                                                                    | 66.7                                                             | 660                                                       | 1.27                                            |

| Guaranteed control range for the amplitude              | 60 120                                                                 | 40 80                                                            | 400 800                                                   | 0.76 1.52                                       |

| Setting range of the amplitude controller               | 56 168 <sup>1)</sup>                                                   | 38 112 <sup>1)</sup>                                             | 370 1110 <sup>1)</sup>                                    | 0.71 2.13 1)                                    |

| Vector monitoring <sup>2)</sup>                         | 30                                                                     | 20                                                               | 200                                                       | 0.38                                            |

| Guaranteed control range for the offset (sensor)        | ±15                                                                    | ±10                                                              | ±70                                                       | ±0.133                                          |

| Setting range of the offset controller                  | ±25                                                                    | ±17                                                              | ±165                                                      | ±0.315                                          |

<sup>1)</sup> The setting range for the amplitude is greater than the control range of the ADC.

Document: 44800-DB-1-3-E-NIP-AMAC Page: 15/65

<sup>&</sup>lt;sup>2)</sup> An aggregate signal from sine and cosine is monitored. See chapter 7.5 Bit VLOW

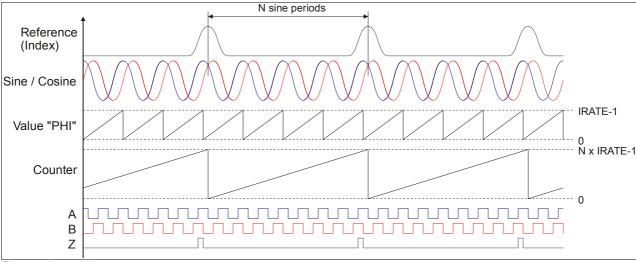

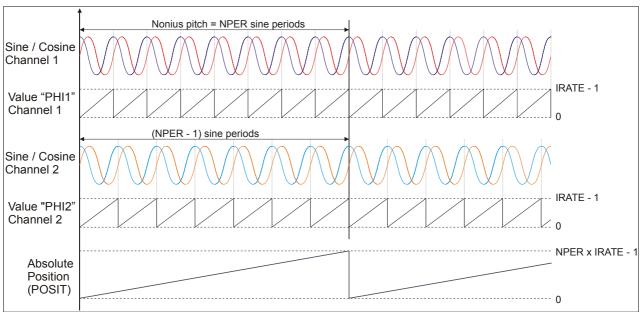

## 7.3 Interpolation / nonius calculation

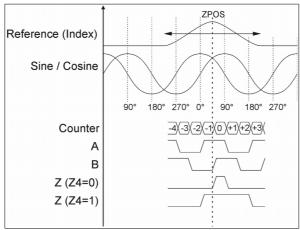

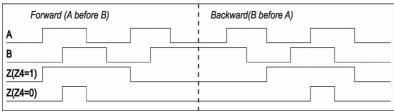

The signal periods of the analog sinusoidal and cosinusoidal signals are divided according to the selected interpolation rate and provided to the serial interfaces (SPI/SSI/BiSS) as phase and count value. In parallel, square-wave sequences with 90° phase shift (A/B/Z signals) are generated.

Figure 5: Interpolation

Using the phase values of the two channels and the vernier scale (nonius) method, the absolute position of the sensor is determined on the measuring scale. Errors of the sensor signal or resulting from inaccuracies of the measuring scale can be suppressed by way of an integrated correction. Therefore, 16 correction coefficients, determined by a software-based calibration algorithm, can be stored in the IC's internal EEPROM.

Figure 6: Nonius calculation

Document: 44800-DB-1-3-E-NIP-AMAC Page: 16/65

Table 14: Operating modes of the GC-NIP

| Mode         | CFG1/Mode'(3:0) | Sensor type           | Measuring value                                                                    | s                                                                                                                                                                                                                                    |

|--------------|-----------------|-----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nonius + ABZ | X000            | Nonius sensor         | Register CNT1:<br>Register CNT2:<br>Register POSIT:<br>SSI/BiSS:<br>ABZ1:<br>ABZ2: | Incremental position channel 1 Incremental position channel 2 Absolute position <sup>1)</sup> Absolute position <sup>1)</sup> Incremental signals channel 1 Incremental signals channel 2                                            |

| Two channel  | X000            | 2 independent sensors | Register CNT1:<br>Register CNT2:<br>Register POSIT:<br>SSI/BiSS:<br>ABZ1:<br>ABZ2: | Incremental position channel 1<br>Incremental position channel 2<br>Incremental position 1 and/or 2 <sup>1)</sup><br>Incremental position 1 and/or 2 <sup>1)</sup><br>Incremental signals channel 1<br>Incremental signals channel 2 |

| Calibration  | 0101            | Nonius sensor         | Register CNT1:<br>Register CNT2:<br>Register POSIT:<br>SSI/BiSS:<br>ABZ1:<br>ABZ2: | Incremental position channel 1 Incremental position channel 2 Absolute position <sup>1)</sup> Absolute position <sup>1)</sup> Test signals for sensor adjustment Test signals for sensor adjustment                                  |

<sup>1)</sup> The content of register POSIT is selected via CFGBiSS/STSEL(1:0) (see Register description)

## 7.3.1 Interpolation rate / nonius pitch

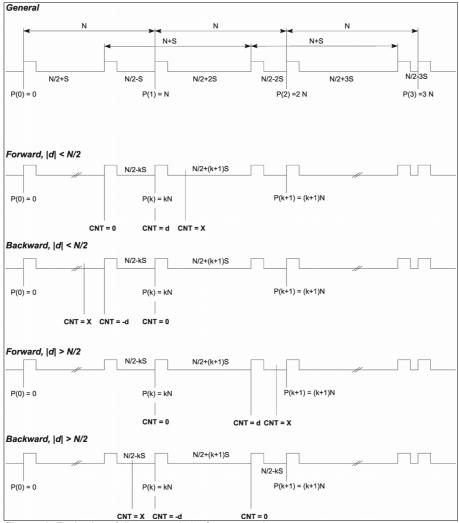

The term 'interpolation rate' (IRATE) is here understood as the number of increments, into which the sinusoidal/cosinusoidal period of the input signals is divided. 'Nonius pitch' describes the number of periods of the input signals, where the absolute position can be clearly assigned using the vernier (nonius) method. Possible interpolation rates for the nonius calculation of the GC-NIP can be selected between 256 and 8192 and must be divisible by 8. Additionally, the interpolation rate for the integrated interpolation counters and the square-wave-signal outputs (A/B) can be divided by a selectable factor (IRDIV) of 1, 2, 4 or 8 (both channels independently). The divided interpolation rate of the incremental counters corresponds the number of signal transitions at the A/B outputs per input signal period. The number of square-wave periods at the outputs A and B amounts to  $\frac{1}{4}$  of the divided interpolation rate. The nonius pitch (NPER) is selectable from the values IRATE/8, IRATE/16, IRATE/32 or IRATE/64.

Following table shows possible combinations and limitations of interpolation rate and nonius pitch for different interfaces and use cases.

Table 15: Selecting interpolation rate and nonius pitch

| Interface / use case           | Interpolation rate                                                                          | Requirement/Limitation                                | Possible values for nonius pitch                                        |

|--------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|

| Singleturn Nonius              | IRATE from EEPROM<br>256 8192                                                               | IRATE is divisible by 8                               | NPER = IRATE / DIV<br>DIV = [8, 16, 32, 64]<br>If DIV = 8: IRATE ≤ 4096 |

| Internal interpolation counter | IRATE from EEPROM / IRDIV IRDIV = [1, 2, 4, 8]                                              | IRATE is divisible by 8                               | No influence                                                            |

| A/B-Output                     | IRATE from EEPROM / IRDIV<br>IRDIV = [1, 2, 4, 8]<br>IRDIV2 = [1, 2, 4, 8] (IRD2SEL<br>= 1) | IRATE is divisible by 8 IRATE/IRDIV is divisible by 4 | No influence                                                            |

Document: 44800-DB-1-3-E-NIP-AMAC Page: 17/65

#### Example 1

The resolution of the absolute position should be at least 17 bit

The IC is used with measuring scales with a nonius pitch of 50 ... 70 (channel 1)

The incremental resolution, using the AB-signals for a motor controller should be at least 10 bit

| <b>NPER</b> | IRATE | DIV | Resolution | Bit   | IRDIV | IRATE (ABZ) | NPER | IRATE | DIV | Resolution | Bit   | IRDIV | IRATE (ABZ) |

|-------------|-------|-----|------------|-------|-------|-------------|------|-------|-----|------------|-------|-------|-------------|

| 50          | 3200  | 64  | 160000     | 17.29 | 2     | 1600        | 61   | 3904  | 64  | 238144     | 17.86 | 2     | 1952        |

| 51          | 3264  | 64  | 166464     | 17.34 | 2     | 1632        | 62   | 3968  | 64  | 246016     | 17.91 | 2     | 1984        |

| 52          | 3328  | 64  | 173056     | 17.40 | 2     | 1664        | 63   | 4032  | 64  | 254016     | 17.95 | 2     | 2016        |

| 53          | 3392  | 64  | 179776     | 17.46 | 2     | 1696        | 64   | 2048  | 32  | 131072     | 17.00 | 2     | 1024        |

| 54          | 3456  | 64  | 186624     | 17.51 | 2     | 1728        | 65   | 2080  | 32  | 135200     | 17.04 | 2     | 1040        |

| 55          | 3520  | 64  | 193600     | 17.56 | 2     | 1760        | 66   | 2112  | 32  | 139392     | 17.09 | 2     | 1056        |

| 56          | 3584  | 64  | 200704     | 17.61 | 2     | 1792        | 67   | 2144  | 32  | 143648     | 17.13 | 2     | 1072        |

| 57          | 3648  | 64  | 207936     | 17.67 | 2     | 1824        | 68   | 2176  | 32  | 147968     | 17.17 | 2     | 1088        |

| 58          | 3712  | 64  | 215296     | 17.72 | 2     | 1856        | 69   | 2208  | 32  | 152352     | 17.22 | 2     | 1104        |

| 59          | 3776  | 64  | 222784     | 17.77 | 2     | 1888        | 70   | 2240  | 32  | 156800     | 17.26 | 2     | 1120        |

| 60          | 3840  | 64  | 230400     | 17.81 | 2     | 1920        |      |       |     |            |       |       |             |

#### Example 2

The maximum resolution for the absolute position should be achieved

The IC is used with measuring scales with a nonius pitch of 30 ... 40 (channel 1)

The maximum interpolation rate for the AB-output is 128. This value has been calculated using the maximum input frequency and the maximum output frequency for the ABZ-outputs (see chapter 7.4).

| <b>NPER</b> | IRATE | DIV | Resolution | Bit   | IRDIV | IRATE (ABZ) | NPER | IRATE | DIV | Resolution | Bit   | IRDIV | IRATE (ABZ) |

|-------------|-------|-----|------------|-------|-------|-------------|------|-------|-----|------------|-------|-------|-------------|

| 30          | 960   | 32  | 28800      | 14.81 | 8     | 120         | 36   | 576   | 16  | 20736      | 14.34 | 8     | 72          |

| 31          | 992   | 32  | 30752      | 14.91 | 8     | 124         | 37   | 592   | 16  | 21904      | 14.42 | 8     | 74          |

| 32          | 1024  | 32  | 32768      | 15.00 | 8     | 128         | 38   | 608   | 16  | 23104      | 14.49 | 8     | 76          |

| 33          | 528   | 16  | 17424      | 14.09 | 8     | 66          | 39   | 624   | 16  | 24336      | 14.57 | 8     | 78          |

| 34          | 544   | 16  | 18496      | 14.17 | 8     | 68          | 40   | 640   | 16  | 25600      | 14.64 | 8     | 80          |

| 35          | 560   | 16  | 19600      | 14.26 | 8     | 70          |      |       |     |            |       |       |             |

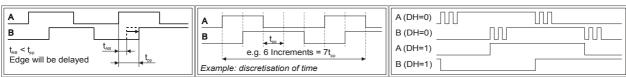

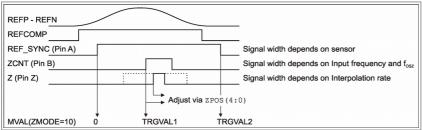

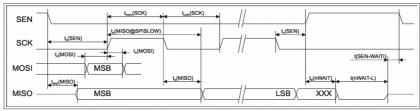

## 7.3.2 Edge distance control / Interval time $t_{pp}$ / Hysteresis